### INITIATION A LA PRATIQUE DE L'ELECTRONIQUE

# LE MULTIPLEXAGE

Les multiplexeurs et démultiplexeurs sont des circuits combinatoires dont l'équivalent mécanique est un commutateur rotatif à plusieurs pôles. Un multiplexeur aiguille successivement plusieurs lignes sur une seule. Le démultiplexeur est le contraire du multiplexeur, il connecte une seule ligne successivement sur plusieurs.

Le circuit de base de ces commutateurs électroniques est constitué par une porte ET. Il y a autant de ces opérateurs que de lignes à commuter. Dans un multiplexeur, la sortie de chaque opérateur est reliée à l'entrée de l'opérateur OU de sortie.

Un circuit annexe sélectionne la ligne choisie. Sa complexité dépend du nombre de voies à commuter. Les multiplexeurs et démultiplexeurs intégrés présentent une entrée « Strobe » utilisée pour la validation.

#### Multiplexeurs et démultiplexeurs

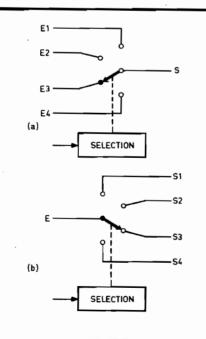

Les multiplexeurs et les démultiplexeurs font partie de la famille des circuits combinatoires. Ce sont des commutateurs électroniques. Leur équivalent mécanique est représenté sur la figure 1.

Un multiplexeur permet de brancher successivement plusieurs voies sur une seule. Un multiplexeur possède plusieurs entrées et une sortie unique. Il comporte un circuit annexe permettant de sélectionner une seule ligne à l'entrée. N'étant constitué que de portes logiques, son fonctionnement s'explique facilement. La figure 1a représente un multiplexeur 4 voies vers une. On l'appelle aussi « multiplexeur 4 bits ».

Un démultiplexeur est le contraire d'un multiplexeur. Il permet de commuter l'unique voie d'entrée sur une seule des sorties suivant la commande imposée par le circuit de sélection.

FIGURE 1 Schéma de principe d'un multiplexeur 4 voies vers 1 (a) et d'un démultiplexeur une voie vers 4.

### Aiguillage électronique

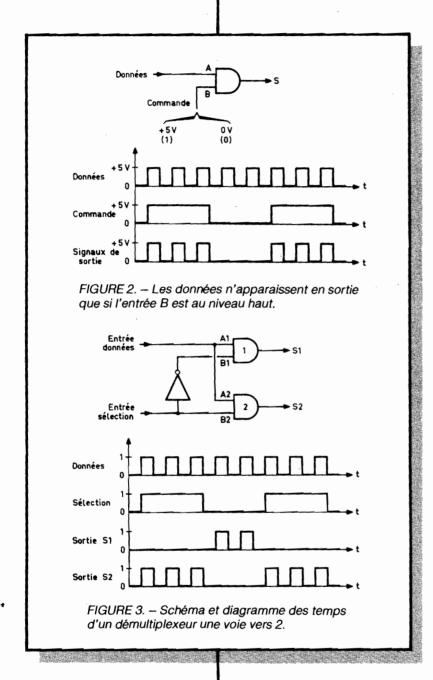

Le circuit de base de ces commutateurs électroniques est constitué par une porte ET. Nous savons que dans ce type de circuit, s'il comporte deux entrées A et B, le niveau bas appliqué sur l'une de celles-ci (le B par exemple) met automatiquement la sortie S au niveau zéro. En revanche, si B = 1, on retrouve en sortie un niveau identique à celui de l'entrée A. Ceci est expliqué sur la figure 2. La donnée appliquée en A n'apparaît en S que si la commande B est reliée au + 5 volts (niveau logique 1)

Si nous avons à transmettre une donnée soit sur une ligne soit sur une autre, nous allons utiliser deux opérateurs ET commandés par un circuit de sélection constitué par un inverseur logique (fig. 3).

Nous voyons que si l'entrée de sélection est au niveau haut, on a  $B_1 = 0$  et  $B_2 = 1$ , ce qui fait que l'information

Nº 1723 - Décembre 1985 - Page 155

ELECTRONIQUE

appliquée à l'entrée du circuit ne sera transmise que sur la ligne branchée sur S<sub>1</sub>.

#### Démultiplexeurs

Le schéma que nous venons de présenter est un décodeur/démultiplexeur une voie vers 2, ou démultiplexeur 2 bits.

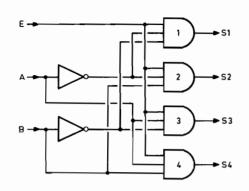

Nous avons sur la figure 4 un démultiplexeur une voie vers 4. La ligne d'entrée des données est appliquée sur les 4 opérateurs ET. Remarquons également que pour commander la commutation de ces 4 circuits il faut 2 entrées pour la sélection, puisqu'en binaire deux quantités A et B permettent quatre possibilités différentes

(rappel:  $2^n = 4$ , sin = 2).

Dans l'éventualité de 8 sorties, il serait nécessaire de disposer d'un circuit de sélection ayant 3 entrées A, B et C (2<sup>3</sup> = 8).

Revenons à notre démultiplexeur à 4 sorties, nous voyons alors que, en plus de l'entrée « donnée », chaque porte possède deux entrées reliées au circuit de sélection. La table de vérité du cir-

cuit est donnée figure 4. Pour chaque ligne de cette table, quel que soit le niveau de A et B, il n'y a qu'une seule porte qui soit passante. Au cas où un train d'impulsions serait présent à l'entrée E, l'état de la sélection étant A = 0 et B = 1, ce train d'impulsions se retrouverait à la sortie S2.

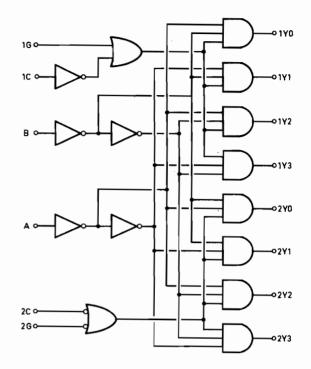

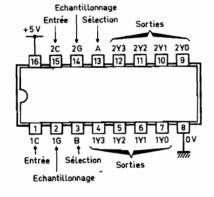

En ce qui concerne les démultiplexeurs intégrés, citons le 74154, circuit TTL à 24 broches effectuant un aiguillage à 16 directions (16 sorties) et le 74155 qui est un démultiplexeur 2 fois une voie vers 4. Son schéma interne et son branchement sont indiqués sur les figures 5 et 6.

L'entrée 1C correspond aux sorties allant de 1Y0 à 1Y3; l'entrée 2C correspond aux sorties 2Y0 à 2Y3. Le même circuit de sélection est employé pour les deux groupes. Les entrées 1G et 2G sont utilisées pour l'échantillonnage (« strobe » en anglais). Ces entrées servent à inhiber chacune des sections suivant les besoins.

Les sorties du 74155 sont des totem-poles. Le circuit TTL du type 74156 a exactement le même schéma interne, mais ses sorties sont en collecteur ouvert.

Une sélection de démultiplexeurs intégrés TTL est donnée sur le tableau I. On y verra que le 74154 démultiplexe 4 voies vers 16. En effet, il a la possibilité de décoder un mot de 4 bits (entrées A, B, C et D) et de le transmettre à une seule des 16 sorties. Les deux entrées « strobe » doivent être alors au niveau bas

Avec ce circuit, le démultiplexage une voie vers 16 s'effectue en rentrant la donnée par l'une des deux entrées du « strobe », la seconde restant au niveau bas. Les entrées A, B, C et D retrouvent alors leur fonction de sélection.

#### Multiplexeur

Comme nous l'avons vu dans le premier paragraphe, ce circuit présente plusieurs entrées et une seule sortie.

Quant à sa constitution, le multiplexeur comprend autant d'opérations ET qu'il y a d'entrées. Un opérateur OU, relié à toutes ces portes ET, transmet la donnée vers la sortie. Le circuit de sélection est identique à celui dont nous avons parlé pour le démultiplexeur.

Page 156 - Décembre 1985 - Nº 1723

| Α | 8 | S1 | S2 | S3 | 54 |

|---|---|----|----|----|----|

| 0 | 0 | Ε  | 0  | 0  | 0  |

| 0 | 1 | 0  | E  | 0  | 0  |

| 1 | 0 | 0  | 0  | Ε  | 0  |

| 1 | 1 | 0  | 0  | 0  | Ε  |

FIGURE 4. – Démultiplexeur 1 voie vers 4 et sa table de vérité.

FIGURE 5. - Schéma interne du démultiplexeur 74155.

FIGURE 6. – Brochage du 74155 (démultiplexeur 2 fois une voie vers 4).

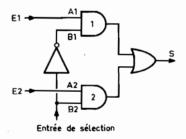

FIGURE 7 Schéma d'un multiplexeur 2 bits.

#### Sélection de multiplexeurs et de démultiplexeurs TTL

| Туре                             | Fonction                                                                                                                                                                 | Boîtier                                              |

|----------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|

| 74150<br>74151<br>74153<br>74157 | Multiplexeur 16 voies vers une Multiplexeur 8 voies vers une (sorties Q et Q) Double multiplexeur 2 fois 4 voies vers une Quadruple multiplexeur 4 fois 2 voies vers une | 24 broches<br>16 broches<br>16 broches<br>16 broches |

| 74154<br>74155<br>74156          | Démultiplexeur 4 voies vers 16 Double démultiplexeur 2 fois une voie vers 4 Double démultiplexeur 2 fois une voie vers 4 (sortie collecteur ouvert)                      | 24 broches<br>16 broches<br>16 broches               |

Un « sélecteur/multiplexeur 2 bits » (ou 2 voies vers une) se compose donc de deux portes ET, d'une porte OU et d'un inverseur logique pour la sélection (fig. 7).

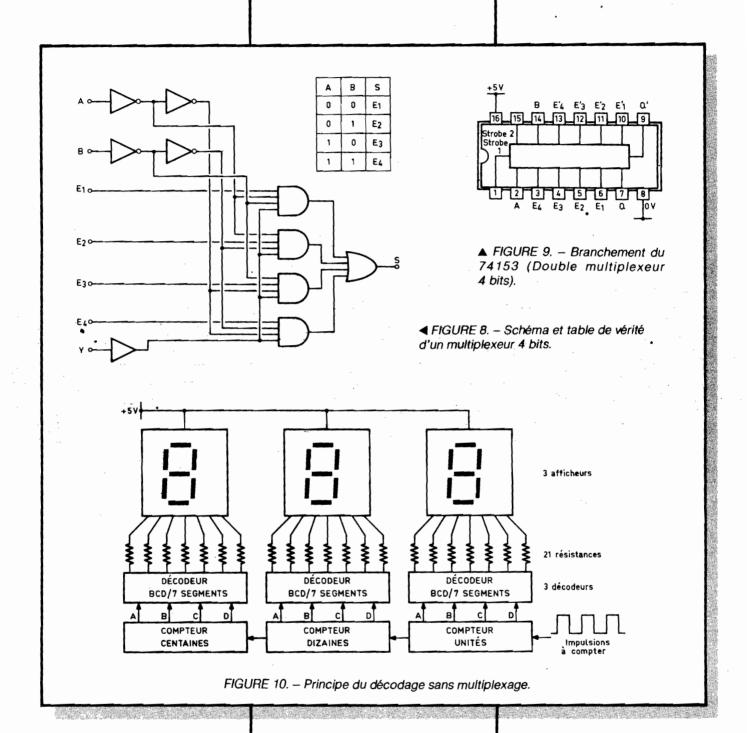

Un multiplexeur 4 voies vers une est composé de 4 portes ET à 3 entrées (une pour la donnée, deux pour la sélection). Le multiplexeur comporte également une porte OU à 4 entrées et un circuit de sélection à deux entrées A et B (fig. 8).

L'entrée Y est utilisée pour la validation. Le signal qui lui est appliqué est souvent appelé « signal de STROBE ».

Nº 1723 - Décembre 1985 - Page 157

ELECTRONIQUE

## Multiplexeurs intégrés

Une sélection de multiplexeurs intégrés est donnée sur le tableau I.

Le schéma interne donné figure 8 est tiré du 74153 qui est un double multiplexeur 4 bits. Son schéma de branchement se trouve sur la figure 9. Le circuit de sélection (entrées A et B) est commun pour les deux sections. La seconde est différenciée par l'indice « prime ».

### Une application de multiplexage

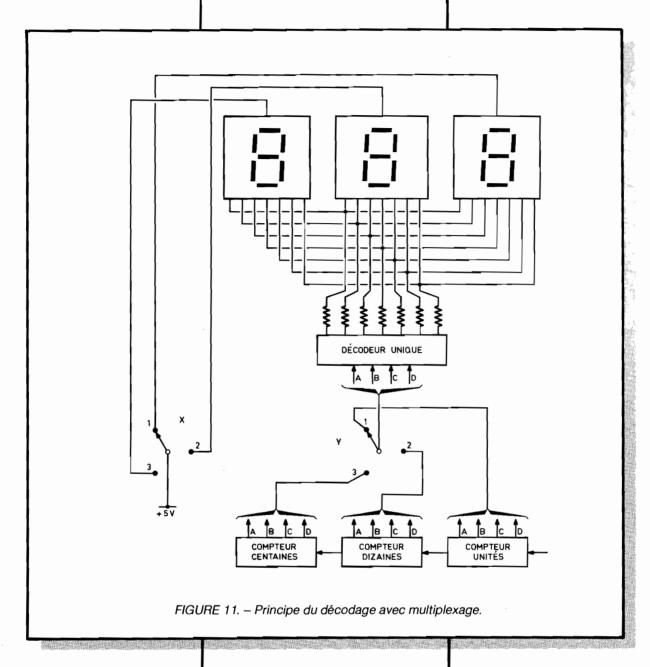

Nous avons choisi l'exemple du multiplexage d'afficheurs 7 segments. Dans *Le Haut-Parleur* d'août 1985, il n'avait été question que d'un seul afficheur. Pour lire le résultat d'un calcul, il nous faut autant d'afficheurs et autant de décodeurs que de chiffres significatifs, sans compter une grande quantité de résistances, ce qui augmente considérablement le nombre de liaisons et le coût du montage.

A partir de 3 ou 4 chiffres, il est préférable d'adopter un affichage multiplexé consistant à n'utiliser qu'un seul

Page 158 - Décembre 1985 - Nº 1723

décodeur et à commuter successivement, et très rapidement, les afficheurs en question.

Cette solution est possible pour deux raisons: d'abord les diodes électroluminescentes ont un temps de réponse très court (elles s'allument et s'éteignent très rapidement). Ensuite, la persistance rétinienne étant inférieure à 1/20° de seconde, l'observateur ne s'aperçoit d'aucun clignotement.

La figure 10 nous montre le schéma d'un circuit sans multiplexage visualisant un comptage de 0 à 999. Nous nous sommes volontairement limités à 3 afficheurs afin de faciliter la compréhension. Dans cette configuration il est nécessaire d'associer au compteur 3 décodeurs et 21 résistances.

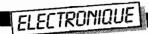

Sur la figure suivante, nous voyons le principe de visualisation multiplexée pour les mêmes 3 afficheurs. Les multiplexeurs sont remplacés ici par leur équivalent mécanique (commutateur rotatif).

Ces commutateurs sont au nombre de deux. L'un branche successivement le + 5 volts sur les 3 anodes, l'autre les informations transmises par l'ensemble des 3 compteurs. Lorsque X est sur la position 1, le commutateur Y se trouve également sur la position 1 (affichage des unités). Puis les curseurs de X et de Y passent sur la position 2 pour l'affi-

chage des dizaines, puis sur la position 3 pour les centaines, pour revenir ensuite sur la position 1. Il est évident que X et Y doivent être synchronisés (évitant ainsi les erreurs d'aiguillage) et tourner rapidement afin d'éviter le papillotement.

On remarque que Y doit commuter les 4 liaisons (A B C D) du compteur considéré. Le schéma de la figure 12 donne davantage de précisions sur la commutation. Cinq commutateurs à 3 positions composent en effet X et Y. Pour plus de clarté du dessin, les liaisons n'ont pas été représentées.

Sur la position 1, l'anode de l'afficheur des unités est la seule alimentée

Nº 1723 - Décembre 1985 - Page 159

et l'entrée du décodeur ne reçoit que A, B, C et D provenant du compteur des unités.

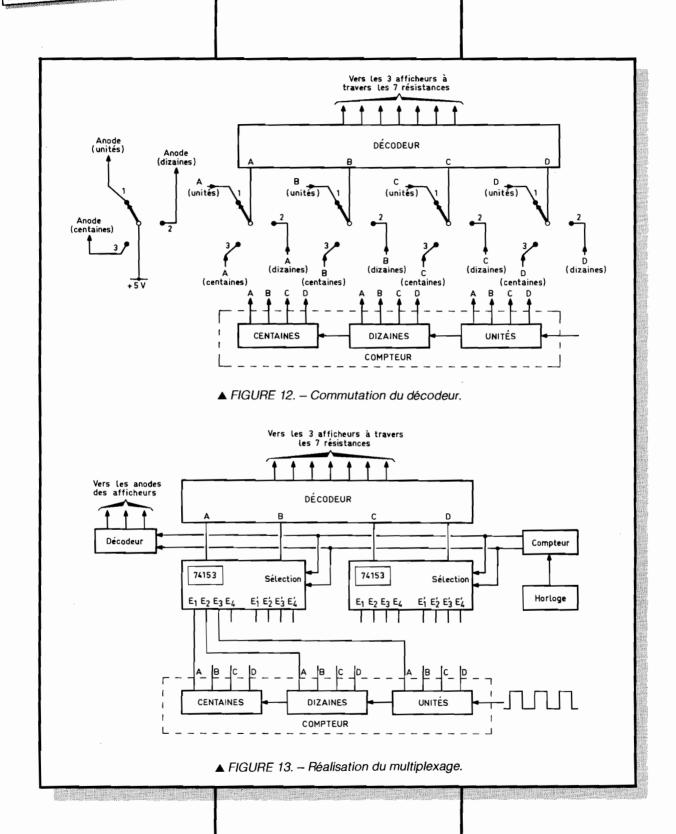

Passons maintenant au schéma avec multiplexeurs. Ce sont ici des 2 fois 4 bits (74153). Pour la clarté nous avons représenté le câblage de l'information A. Les entrées E<sub>4</sub> et E'<sub>4</sub> ne sont pas connectées, elles l'auraient été si le compteur avait été prévu pour compter jusqu'à 9999. Les entrées de sélection sont branchées en parallèle à la sortie d'un compteur binaire donnant successivement les états 00, 01, 11, 00, 01,

etc. Ce compteur est excité par une horloge (un 555) oscillant à une fréquence assez haute pour éviter le papillotement. Ce compteur est également branché sur un décodeur alimentant successivement les 3 anodes de l'afficheur.

J.-B. P.

Page 160 - Décembre 1985 - Nº 1723