## Initiation à la pratique de l'électronique

# LES PORTES LOGIQUES

En résumé, vous allez apprendre ce mois-ci...

Le niveau logique d'entrée appliqué à une porte peut être une tension continue ou un signal rectangulaire.

La porte ET donne un niveau logique 1 à sa sortie X si ses entrées A et B sont à l'état 1.

La formule de la fonction ET s'écrit : X = A.B.

Le logigramme électrique d'une porte ET se compose d'interrupteurs en série.

La porte OU donne un niveau 1 en sortie si l'entrée A ou l'entrée B est au niveau 1.

La formule de la fonction OU est : X = A + B.

L'équivalent électrique d'une porte OU se représente par des interrupteurs en parallèle.

La fonction NON, appelée aussi « négation » ou « inversion » se matérialise par un inverseur.

La formule de la fonction NON s'écrit simplement :  $X = \overline{A}$ , dont la barre indique l'inversion. On dit que X est le complément de A.

Si l'entrée unique A d'une porte NON est au niveau 1, sa sortie X se trouve au niveau 0. Inversement, lorsque A = 0, X = 1

La fonction NON est réalisée par un transistor monté en émetteur commun.

La fonction NAND se compose d'une porte ET suivie d'un inverseur.

Si les entrées A et B de la porte NAND sont au niveau logique 1, la sortie X est à l'état 0. Dans tous les autres cas, X = 1

La formule de la fonction NAND est  $X = \overline{A.B.}$

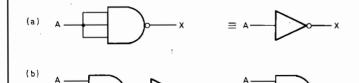

Une porte NAND est équivalente à un inverseur si ses entrées sont toutes reliées ensemble.

Une porte NAND suivie d'un inverseur est équivalente à un circuit ET.

Des fonctions plus complexes s'obtiennent en connectant ensemble plusieurs portes.

Il ne faut jamais relier ensemble plusieurs sorties de portes TTL.

#### La fonction ET

En guise d'introduction, nous avons présenté le mois dernier la fonction ET. Nous avons vu qu'une porte ET pouvait se représenter sous forme mécanique (interrupteurs en série), électrique (avec des diodes) ou électronique (avec un circuit intégré).

Dans la vie courante, nous rencontrons beaucoup d'événements se rapportant à cette fonction. Citons les portes d'une rame de métro, le train ne peut démarrer que si elles sont toutes fermées.

Sur un circuit intégré

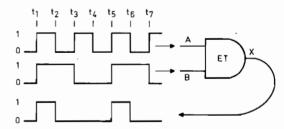

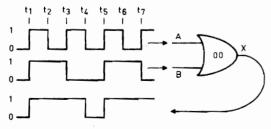

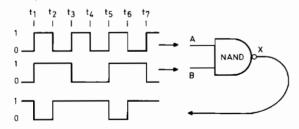

TTL, toutes les entrées doivent être au niveau 1 pour recueillir, en sortie également, un « 1 ». Vous avez pu expérimenter une porte logique ET avec un circuit 7408 placé sur une plaque de connexion. En branchant des tensions de + 5 V (état logique 1) sur les entrées, l'état de la sortie peut être contrôlé par une diode électroluminescente. Ces tensions sont statiques, nous pouvons les remplacer par des signaux rectangulaires d'amplitude + 5 V, comme cela est montré sur la figure 1. L'impulsion positive de sortie obéit à la loi : X = A.B.

Fig. 1. — Les signaux rectangulaires appliqués aux entrées ne donnent un niveau 1 en sortie que pendant le temps  $T_1$ ,  $T_2$  et  $T_5$ ,  $T_6$  pendant lesquels A=B=1.

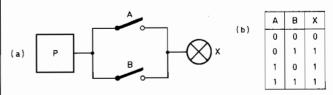

Fig. 2. – Logigramme électrique d'une porte OU (en a) et sa table de vérité (b).

#### La fonction OU

Pour la démonstration, nous gardons les mêmes composants (pile, lampe et deux interrupteurs), mais en disposant cette fois-ci les interrupteurs en parallèle, le fonctionnement du circuit est complètement changé (fig. 2a). Il suffit qu'un seul interrupteur soit fermé pour que la lampe soit allumée. En d'autres termes, il faut que : A = 1ou B = 1 pour que X = 1. Nous sommes en présence d'un circuit logique OU. En étudiant les quatre possibilités d'ouverture et de fermeture des deux interrupteurs, nous constatons que c'est pour seulement A = B = 0 que nous avons X = 0, ce qui est résumé dans la table de vérité de la figure 2b.

Cette fonction OU s'exprime par la relation :

X = A + B

(se lisant : « X égal A ou B »).

Le signe X est parfois remplacé par la lettre V: X = A V B, mais cette écriture devient de plus en plus rare.

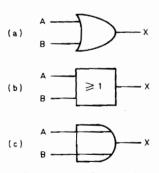

Au point de vue représentation schématique, nous donnons, figure 3, le symbole le plus courant (a) que nous adopterons par la suite, celui créé par l'AF-NOR (b); c'est un carré dans l'intérieur duquel l'expression nous rappelle que pour avoir en sortie le niveau 1, il suffit qu'au moins une seule entrée soit à ce niveau. Le troisième symbole est ici pour mémoire, on ne le rencontre presque plus.

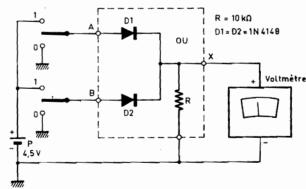

Une porte peut être commandée, non pas seulement par des interrupteurs, mais par des tensions branchées à ses entrées. L'intérieur de cette porte pourrait être composé de diodes et d'une résistance (fig. 4).

Nous voyons que si les

deux entrées sont au potentiel de la masse (0 V), ce qui correspond à la première ligne de la table de vérité, aucun courant ne peut traverser les diodes puisqu'elles ne se trouvent pas polarisées (anode et cathode au même potentiel). La sortie X reste donc à l'état zéro, l'aiguille du voltmètre branché en X ne dévie pas.

En revanche, si un seul des points A ou B est relié au pôle positif de la pile P. la diode en question est polarisée dans le sens direct (anode positive par rapport à la cathode) et un courant traverse le circuit série comprenant la diode et la résistance. Ce courant traversant R fait apparaître aux bornes de celle-ci une tension (point X positif). Cette tension, mesurée par le voltmètre, est présente si A ou B reste au niveau 1.

La figure 5 nous montre une porte OU commandée

par des signaux rectangulaires.

La porte OU est parfois désignée dans les textes français par son appellation anglaise OR.

Il est bon de se souvenir que de même qu'une fonction ET peut être comparée à un circuit dans lequel deux interrupteurs sont disposés en série, une fonction OU nous rappelle plusieurs interrupteurs en parallèle.

Exemple de fonction OU dans la vie courante : éclairage de la cage d'escalier d'une maison à plusieurs étages, la lumière s'obtient par la commande de l'interrupteur du rez-de-chaussée, ou par celui de n'importe quel étage.

## Fonction OU intégrée

En technique TTL, cette fonction se trouve dans le

Fig. 3. – Représentation symbolique d'une porte OU – En (a) la plus courante, en (b) la normalisée et en (c) une représentation périmée.

Fig. 4. – Porte OU réalisée avec des diodes et une résistance.

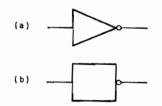

Fig. 7. – Les deux représentations d'un inverseur logique. Symbole courant (a) et normalisé (b). C'est le cercle qui indique la présence de la négation.

Fig. 5. — Le niveau en sortie est à l'état 1, lorsque A=1 ou B=1.

Fig. 6. – Schéma électrique (vu de dessus) Fig. 8. – Tod'un circuit TTL 7432 (4 portes OU à 2 entrées). l'inverseur.

| Α | х |

|---|---|

| 0 | 1 |

| 1 | 0 |

Fig. 8. – Table de vérité de s). l'inverseur.

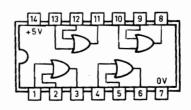

type 7432, comportant 4 portes OU à deux entrées (fig. 6).

#### **Fonction NON**

Appelée aussi « négation » ou « inversion », elle s'exprime par la relation :  $\overline{X} = \overline{A}$

(se lisant: « X égal A barre ») qui signifie simplement que l'état de X est le contraire ou le complément de celui de A. Ses représentations schématiques sont données sur la figure 7. Le cercle situé en sortie de ce circuit indique une négation dans les schémas de circuits logiques.

La table de vérité est très réduite puisque cette porte ne comporte qu'une seule entrée (fig. 8).

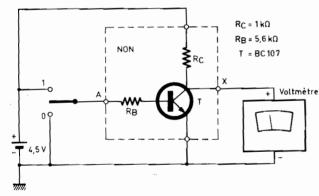

La réalisation pratique de cette fonction se fait avec un transistor monté en collecteur commun (fig. 9).

Les deux possibilités sont les suivantes. D'abord A = 0, la base se trouve reliée au 0 V, le transistor n'est pas polarisé, il ne conduit pas, donc pas de courant dans  $R_c$ . Chute inexistante aux bornes de  $R_c$ . La tension en X est égale à la tension d'alimentation (X = 1).

L'autre cas est : A = 1, le transistor est passant, il y a chute de tension dans R<sub>c</sub>, le voltmètre indique une tension pratiquement égale à zéro.

Exemple de fonction NON dans la vie courante : les dispositifs de sécurité dans certaines machines. Un lave-linge ne peut fonctionner que si la porte de chargement est fermée.

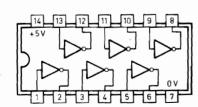

## Fonction NON intégrée

Le circuit TTL 7404 comporte six inverseurs (fig. 10).

#### **Fonction NAND**

Voici une autre fonction un peu particulière. Son nom provient de la contraction de l'anglais « NO-AND » dont la traduction française est « NON-ET ».

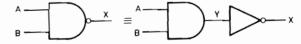

Cette fonction peut être obtenue par une porte ET suivie d'un inverseur NON (fig. 11).

Pour établir la table de vérité, on s'occupe d'abord de la fonction ET (Y = A.B) et on complémente ensuite la sortie  $Y (X = \overline{Y})$  (fig. 12).

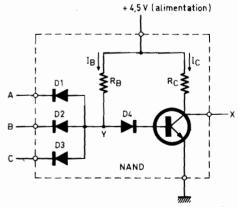

En ce qui concerne la réalisation pratique, nous pourrions très bien utiliser des diodes suivies d'un transistor monté en émetteur commun, comme indiqué sur la figure 13.

Quelques mots sur le fonctionnement du montage: si les trois entrées (A, B, C) sont reliées au pôle « plus » de l'alimentation (4,5 V), ces trois entrées se trouvent être au niveau 1. La cathode et l'anode des diodes correspondantes sont pratiquement au même potentiel puisque les anodes sont reliées en permanence au + 4,5 V à travers R<sub>B</sub>. La

résistance interne des diodes est donc considérée comme étant infinie et les trois diodes sont équivalentes à un circuit ouvert. Seule la diode D<sub>4</sub> est conductrice, elle laisse passer le courant de polarisation l<sub>B</sub> du transistor provenant du + 5 V à travers la résistance R<sub>+</sub>. Le transistor est de ce fait saturé. Le courant le est tel que la chute de tension aux bornes de R<sub>c</sub> est proche de 4,5 V, ce qui fait que la tension en X est voisine de O V (état logique O).

Il suffit qu'une seule entrée soit au potentiel de la masse (niveau 0) pour que le point Y soit à une tension égale à la tension directe de la diode. Cette tension de + 0,6 V bloque le transistor, puisque la tension sur la base de celuici est très faible (inférieure à la tension de seuil). Aucun courant ne traverse R<sub>c</sub>, la totalité de la tension d'alimentation se retrouve sur le collecteur, et le point X est au niveau 1.

Fig. 9. – L'inversion logique peut être réalisée par un simple transistor monté en émetteur commun.

Fig. 10. – Schéma interne d'un 7404 (6 inverseurs).

| Α | В | Υ | Х |

|---|---|---|---|

| 0 | 0 | 0 | 1 |

| 0 | 1 | 0 | 1 |

| 1 | 0 | 0 | 1 |

| 1 | 1 | 1 | 0 |

Fig. 12. – Table de vérité de la fonction NAND.

Fig. 11. — Un NAND est équivalent à un ET suivi d'un inverseur.

Fig. 13. – Réalisation pratique d'un NAND avec des diodes, des résistances et un transistor (technique DTL et non TTL).

La fonction NAND s'exprime par la formule :  $X = \overline{A.B}$

et sa représentation schématique est donnée figure 14.

La figure 15 nous montre un NAND attaqué par des signaux rectangulaires.

Une application d'une fonction NAND pourrait être encore un dispositif de sécurité. X pourrait commander l'alimentation en énergie d'une ligne de chemin de fer à voie unique. Celle-ci est alimentée en permanence, elle ne l'est pas que dans un seul cas: lorsque deux trains A et B s'y engagent en même temps (A = 1, B = 1, X = 0).

Pour terminer, remar-

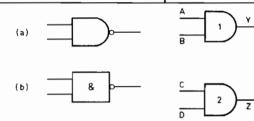

quons qu'avec des portes du type NAND, on réalise des inverseurs. Il suffit de connecter ensemble les entrées. De même, on retrouve une porte ET en faisant suivre un NAND par un inverseur (fig. 16).

#### Fonction NAND intégrée

De nombreuses portes NAND existent en circuit TTL, nous n'en citerons que quatre :

7400 (comportant 4 NAND à 2 entrées)

7410 (triple NAND à 3 entrées)

7420 (double NAND à 4 entrées)

7430 (un seul NAND à 8 entrées).

Fig. 14. – Symbole courant (a) et normalisé (b) d'une porte NAND.

Fig. 17. – Assemblage des portes donnant X = A.B + CD.

Fig. 15. – La sortie X est toujours à l'état 1, sauf lorsque A=1 et B=1 (temps  $E_1,\,T_2$  et  $T_5,\,T_6$ ).

Fig. 16. – En (a) un inverseur réalisé avec un NAND. En (b) un ET obtenu avec un NAND suivi par un inverseur qui pourrait lui aussi être un NAND, dont les entrées seraient reliées comme en (a).

#### Assemblage des portes

Une porte NAND se compose d'un ET suivi par une négation. Nous pouvons imaginer d'autres assemblages et en trouver l'équation équivalente.

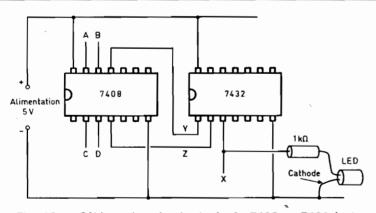

Prenons quelques exemples pour commencer. Sur la figure 17, nous voyons trois portes numérotées de 1 à 3. A la sortie des deux premières, nous avons respectivement : Y = A.B. et Z = C.D. Ces deux sorties Y et Z sont reliées à l'entrée de la porte OU. En X nous avons X = A.B +C.D (« A et B ou C et D »). Puisqu'il y a 4 entrées, nous avons 24 (= 16) combinaisons possibles à l'entrée et pouvons dresser la table de vérité.

Elle comportera 16 lignes de plusieurs colonnes: quatre colonnes pour A, B, C et D, deux colonnes pour Y (= A.B) et Z (= C.D) et une colonne pour la sortie X (= Y + Z). Cette = D = C.D. Et est 4'e est 4'e ces ex lesquel ex 1'e ex 2'e ex 2'e

table de vérité est donnée sur la figure 18.

Nous remarquons que dans la colonne Y, nous avons 1 seulement s'il existe un 1 dans les colonnes A et B (lignes 13 à 16). Le raisonnement est identique pour la colonne Z. En ce qui concerne la colonne X, le niveau 1 apparaît lorsque Y = 1 ou Z = 1.

Finalement nous voyons qu'il y a 7 moyens d'avoir un 1 en sortie.

Sur la ligne 4, X = 1 si A = B = 0 et C = D = 1, l'équation de cette ligne peut s'écrire : X = A.B + C.D, ce qui veut dire que X = 1 à la condition que les entrées A et B soient au niveau zéro ou que les entrées C et D soient au niveau un.

De même sur la ligne 8, nous avons : A = 0, B = C= D = 1, soit  $X = \overline{A}$ .B. +

Et l'équation générale est l'ensemble de toutes ces expressions de X pour lesquelles nous avons un « 1 »:

$$Y = (\overline{A}.\overline{B} + C.D) + (\overline{A}.B + C.D) + (\underline{A}.\overline{B} + C.D)$$

$$+ (\underline{A}.B + \overline{C}.\overline{D}) + (\underline{A}.B + \overline{C}.D) + (\underline{A}.B + C.\overline{D})$$

$$+ (\underline{A}.B + C.D).$$

| 16                                                                                  |                                     |                                                               |                                                                    |                                                          |                                           |                                                     |                                                |

|-------------------------------------------------------------------------------------|-------------------------------------|---------------------------------------------------------------|--------------------------------------------------------------------|----------------------------------------------------------|-------------------------------------------|-----------------------------------------------------|------------------------------------------------|

|                                                                                     | Α                                   | В                                                             | С                                                                  | D                                                        | Y<br>(= A.B)                              | (= C.D)                                             | (= X<br>(= Y.Z)                                |

| 1<br>2<br>3<br>4<br>5<br>6<br>7<br>8<br>9<br>10<br>11<br>12<br>13<br>14<br>15<br>16 | 0 0 0 0 0 0 0 1 1 1 1 1 1 1 1 1 1 1 | 0<br>0<br>0<br>0<br>1<br>1<br>1<br>0<br>0<br>0<br>1<br>1<br>1 | 0<br>0<br>1<br>1<br>0<br>0<br>1<br>1<br>0<br>0<br>1<br>1<br>0<br>0 | 0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1 | 0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0 | 0<br>0<br>0<br>1<br>0<br>0<br>0<br>1<br>0<br>0<br>0 | 0<br>0<br>0<br>1<br>0<br>0<br>0<br>1<br>0<br>0 |

|                                                                                     | 1                                   |                                                               |                                                                    | I                                                        |                                           |                                                     |                                                |

Fig. 18. - Table de vérité du premier exemple (voir texte).

Plus tard, nous vous indiquerons comment simplifier une telle expression.

Si vous possédez un 7408, un 7432, une résistance 1 kΩ, une diode électroluminescente et une plaque de connexions, vous pouvez facilement contrôler la table de vérité. Il suffit de brancher les entrées A, B, C et D suivant le cas sur la ligne +5 V (niveau 1) ou sur la ligne 0 V (niveau 0). Le schéma de branchement est indiqué sur la figure 19. Le schéma interne du 7408 a été donné le mois dernier.

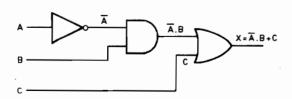

Comme deuxième exemple, nous prendrons le problème inverse. L'expression a obtenir est:  $X = \overline{A}.B + C$ . Nous voyons que nous avons besoin d'une porte OU à deux entrées, d'une porte ET également à deux entrées, ainsi que d'un inverseur pour l'entrée A. Le schéma du circuit est donné sur la figure 20. Vous pouvez dresser la table de vérité. Puisque le

montage possède 3 entrées, cette table doit avoir 2³ soit 8 lignes. Quant au nombre de colonnes, il sera prudent d'en prévoir 6 : trois pour les entrées, une pour  $\overline{A}$ , une pour la sortie de la porte ET  $(\overline{A}B)$  et enfin la dernière pour la sortie X.

Il serait également intéressant de réaliser le montage avec 3 circuits intégrés (7404, 7408 et 7432) comme vous l'avez fait avec le montage précédent.

## Quelques détails pratiques

Avec les manipulations précédentes, vous avez pu vous rendre compte par vous-même que, premièrement, les circuits TTL ne coûtent vraiment pas chers par rapport aux autres composants, et que, deuxièmement, les circuits TTL sont d'un emploi très facile.

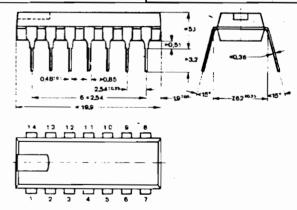

Mais il faut cependant être assez prudent en les manipulant. Ces précautions portent d'abord sur la mise en place du circuit intégré sur son support. Il faut que les deux rangées de broches soient bien alignées et distantes entre elles de huit millimètres environ. L'espace entre deux broches consécutives doit être de 2,5 mm (fig. 21).

Les broches se retrouvent redressées en mettant sur champ le circuit intégré et en appuyant la rangée de broches sur une surface dure. Ainsi le circuit pourra être facilement enfiché sur son support.

Pour le retirer, on le soulèvera avec précaution en le prenant entre le pouce et l'index. Et si cela s'avère difficile l'extraction se fera en utilisant une lame de tournevis insérée entre le circuit et la plaque, parallèlement aux deux rangées de broches.

Nous avons déjà parlé des limites de tension à appliquer au circuit TTL. Sans rentrer dans des détails technologiques, il est primordial de savoir, lorsqu'on manipule des TTL, que deux sorties de portes ne doivent jamais être reliées ensemble. Une exception est faite en ce qui concerne les TTL dits « à collecteur ouvert ». Nous en reparlerons plus tard.

## Exercices d'application

Nous vous proposons deux exercices dont nous vous donnerons la solution le mois prochain.

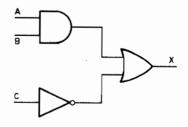

- 1) Quel est le schéma du circuit logique dont l'expression est : A.B + A.B?

- 2) Quelle est la formule du circuit représenté sur la figure 22 ?

J.-B.P

Fig. 19. - Câblage des circuits intégrés 7408 et 7432 (voir texte).

Fig. 21. - Dimensions d'un circuit intégré 14 broches.

Fig. 20. - Schéma du deuxième exemple.

Fig. 22. - Schéma du deuxième exercice.