# Boucle à verrouillage de phase à large bande

par G. NORMAND (\*)

L'article suivant décrit le principe théorique d'une boucle à verrouillage de phase dite d'offset capable de fonctionner sur une large dynamique de fréquence. Un exemple de réalisation en technologie C-MOS est présenté accompagné des résultats des mesures effectuées sur le prototype réalisé.

### Principe de la boucle PLL d'offset

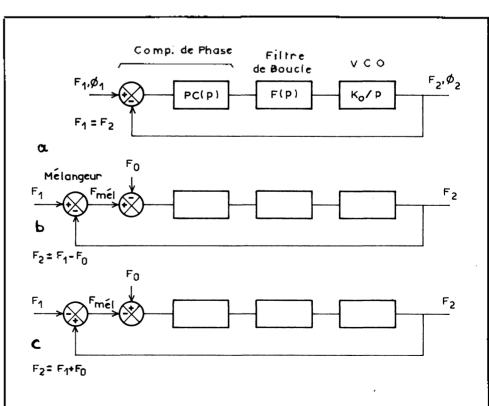

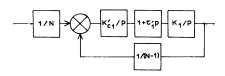

Une boucle à verrouillage de phase (PLL) du type analogique comporte essentiellement un comparateur de phase, un filtre de boucle et un oscillateur contrôlé en tension ou courant (VCO/CCO). Le modèle linéarisé d'une telle boucle, à retour unitaire, est représenté en notation symbolique par la figure 1a.

Une boucle PLL d'offset permet d'effectuer une translation de fréquence sur un signal de fréquence donnée F<sub>1</sub> d'une quantité F<sub>0</sub> faible devant F<sub>1</sub>. La figure 1b représente le modèle linéarisé d'une boucle d'offset où la translation de fréquence se fait vers les fréquences décroissantes:

$$\mathsf{F}_2 = \mathsf{F}_1 - \mathsf{F}_0,$$

pendant que la translation vers les fréquences croissantes s'opère seion la figure 1c :

$$F_2 = F_1 + F_0.$$

La boucle d'offset s'obtient en plaçant un mélangeur (Mixer) devant le comparateur de phase.

# Comportement d'un mélangeur

Les fréquences F<sub>1</sub> et F<sub>2</sub> reçues par le mélangeur sont supposées voisines l'une de l'autre. La sortie délivre, après un éventuel filtrage, un signal dont la fréquence F<sub>mél</sub> est la différence des fréquences incidentes :

$$\mathbf{F}_{\text{mét}} = |\mathbf{F}_1 - \mathbf{F}_2| \tag{1}$$

De la même façon, la phase instantanée en sortie est la différence des phases incidentes :

$$\Phi_{\text{méi}} = |\Phi_1 - \Phi_2|.$$

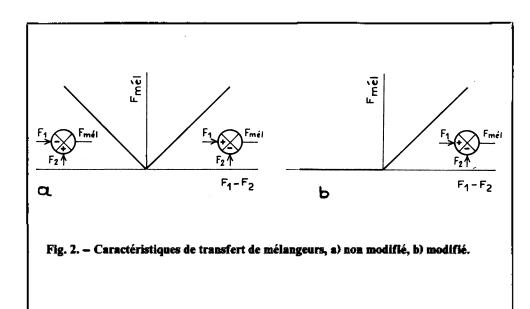

La figure 2a représente la caractéristique de transfert du mélanger classique, que l'on peut encore écrire :

$$F_{méi} = \begin{cases} F_1 - F_2, pour F_1 > F_2, \\ F_2 - F_1, pour F_1 < F_2. \end{cases}$$

Fig. 1. – Modèles linéaires de boucles à verrouillage de phase, a) élémentaire, b) et c) d'offset.

<sup>(\*)</sup> Laboratoire de Physique des Matériaux et Composants pour l'Électronique de Nantes.

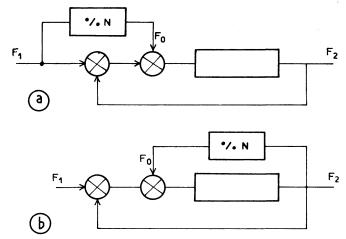

Fig. 3. — Fréquence

F2 d'offset issue par

division, a) de la

fréquence d'entrée,

b) de la fréquence de

sortie.

Cela signifie que le mélangeur constitue un sommateur/soustracteur de fréquence (et de phase) doté de deux entrées : l'une non inverseuse, l'autre inverseuse, affectées respectivement aux fréquences d'entrée : l'une, la plus élevée, l'autre, la plus faible. Supposons que l'une, F<sub>1</sub> soit fixe (fréquence d'entrée de la boucle d'offset) et l'autre, F2, varie autour de F1 (fréquence de sortie de la boucle lors de la recherche du verrouillage), et que F2 passe d'une valeur inférieure à F<sub>1</sub> pour laquelle la boucle était en contre-réaction vers une valeur supérieure à F<sub>1</sub>. Alors la boucle tombe dans un état de réaction positive puisque la nature inverseuse ou non inverseuse des entrées du mélangeur est échangée. Le plus souvent dès lors, la boucle s'éloigne de sa position d'équilibre (verrouillage).

Les mélangeurs les plus utilisés sont les multiplicateurs analogiques, les modulateurs/démodulateurs, les diodes mélangeuses, des circuits logiques comme par exemple la bascule D.

## Boucle d'offset large bande

On évite en général l'inversion de polarité des entrées du mélangeur en limitant la dynamique en fréquence du VCO et en y excluant la fréquence d'entrée F<sub>1</sub>. Cela revient à se limiter à :

- une faible dynamique en fréquence sur l'entrée ;

- un écart des fréquences

$|F_1 - F_2|$  pas trop faible devant la dynamique du VCO.

La boucle d'offset large bande typique que l'on cherche à matérialiser est schématisée par la figure 3 sur laquelle la fréquence d'offset F<sub>0</sub> est obtenue par division soit de la fréquence d'entrée F<sub>1</sub>, soit de la fréquence de sortie F<sub>2</sub> et sur laquelle les polarités des mélangeurs et des comparateurs de phase sont à déterminer selon la figure 1. On arrive ainsi aux quatre possibilités:

$$F_2 = \frac{N \pm 1}{N} F_1$$

, pour  $F_1 = N F_0$ , (2)

$$F_2 = \frac{N}{N \pm 1} F_1$$

, pour  $F_2 = N F_0$ . (3)

De cette façon, après verrouillage, les fréquences restent dans un rapport constant.

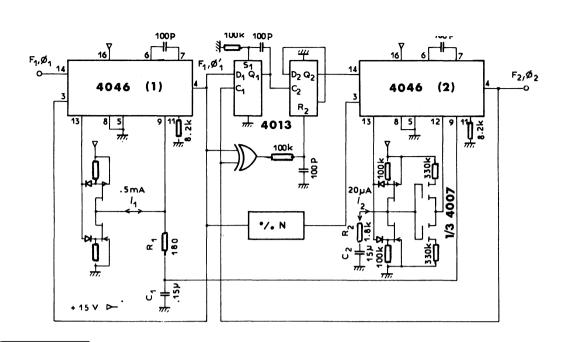

La réalisation proposée (fig. 4) comporte deux circuits intégrés PLL 4046. On y trouve successivement une boucle PLL simple à retour unitaire constituée par le premier circuit intégré suivie de la boucle d'offset proprement dite. Les comparateurs de phase utilisés sont à coïncidence. Ils sont inclus chacun dans les boîtiers 4046.

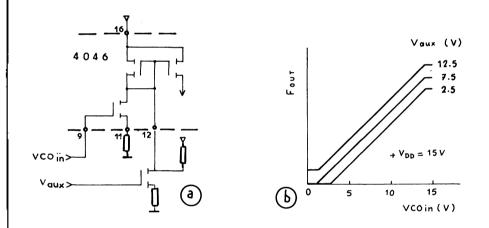

Les deux VCO étant polarisés de la même façon, le rôle de la première boucle PLL est de contrôler en fréquence le second VCO. Ainsi, sur une large dynamique de fréquence à l'entrée, l'écart de fréquence entre la fréquence d'entrée F<sub>1</sub> et la fréquence libre F(VCO<sub>in</sub>) du deuxième VCO reste faible même en dehors du verrouillage. A cet effet, le second VCO est contrôlé en fréquence par deux tensions VCO<sub>in</sub> et V<sub>eux</sub>:

VCO<sub>in</sub>, tension de contrôle issue de la première boucle de phase, est envoyée simultanément sur les entrées de contrôle habituelles des deux VCO. Elle réalise un accord grossier du second sur le premier;

V<sub>aux</sub>, tension de contrôle auxiliaire ou d'asservissement en phase, provient, après filtrage, du comparateur de phase de la boucle d'offset. Elle est appliquée à l'entrée du circuit de contrôle auxiliaire constitué d'un étage MOS complémentaire travaillant en convertisseur tension-courant. Une réalisation simplifiée de ce circuit est donné en figure 5a ainsi qu'un détail du VCO. Le MOS complémentaire procure une excellente linéarité de la réponse en fréquence du VCO à V<sub>aux</sub>, VCO<sub>in</sub> donné, et faci-lite la polarisation de V<sub>aux</sub> autour de la demi-tension d'alimentation sur toute la dynamique du système. La figure 5b décrit la réponse en fréquence du VCO à VCO<sub>in</sub> et  $V_{aux}$ . Ici la constante de gain du VCO,  $K_0 = 2\pi\Delta F_{out}/\Delta V_{aux}$ , est positive. On pourrait aisément la rendre néga-

La dynamique apparente du VCO de la boucle d'offset est donc réduite et de ce fait, il en est de même de sa constante de gain K<sub>0</sub>. On ne peut réduire cette dynamique et K<sub>0</sub> au delà de certaines limites sous peine d'accroître inconsidérablement le temps de réponse de la boucle. Pour un écart relatif faible entre F<sub>1</sub> et F<sub>2</sub> (N élevé), la fréquence F<sub>1</sub> risque d'être incluse dans la bande des fréquences du second VCO, principalement aux basses fréquences. Pour

éviter qu'une réaction positive ne puisse s'établir, on modifie le mélangeur pour qu'il ne réponde qu'à une polarité donnée de la fréquence différentielle F<sub>1</sub> — F<sub>2</sub> (fig. 2b). Envisageons lès cas où les formes d'onde ont un rapport cyclique quelconque puis un rapport cyclique voisin de 50 %.

#### Rapport cyclique quelconque

Fig. 4. – Réalisation de la boucle d'offset large bande.

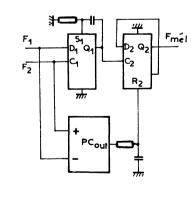

Le mélangeur modifié est constitué d'une double bascule D 4013 et d'un comparateur coıncidence ou comparateur phase/fréquence 4046 ou 4568 (fig. 6). Le comparateur à coîncidence possède deux entrées polarisées activées sur les fronts positifs des signaux incidents, une sortie PCout qui évolue, dans le mode de fonctionnement en comparateur de fréquence, entre le niveau H et l'état haute impédance Z lorsque la fréquence différentielle appliquée entre l'entrée + et l'entrée - est positive. La sortie évolue entre le niveau L et l'état Z dans le cas contraire. On voit (fig. 6) que si  $F_1 > F_2$ , la fréquence différentielle est négative, l'entrée Reset R2 de la deuxième bascule D reste au niveau bas, le mélangeur fonctionne normalement. Si  $F_1 < F_2$ ,  $R_2$  s'établit au niveau haut, la sortie Q2 reste au niveau bas, le mélangeur est inhibé, la fréquence en sortie est nulle.

#### Rapport cyclique voisin de 50 %.

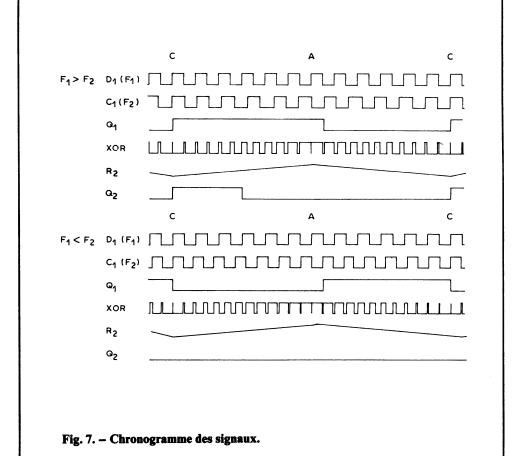

Le comparateur phase/fréquence est remplacé par un simple OU exclusif, XOR. La figure 7 décrit les chronogrammes des signaux. Le si-

Fig. 5. - a) Réalisation simplifiée du contrôle auxiliaire et détail du VCO, b) Réponse du VCO au double contrôle.

gnal issu de XOR, filtré, produit une onde triangulaire au rythme de F<sub>1</sub> - F<sub>2</sub> I, que reçoit R<sub>2</sub>. La sortie Q<sub>1</sub> de la première bascule présente une onde carrée injectée sur l'horloge C<sub>2</sub> de la seconde bascule. Suivant que F<sub>1</sub> — F<sub>2</sub> est positif ou négatif, les fronts positifs en Q1 et C2 apparaissent aux instants de coïncidence C ou d'anticoïncidence A des signaux d'entrée. Dans le premier cas les fronts d'horloge en C2 sont accompagnés d'un niveau bas en R<sub>2</sub> et sont transmis en Q2. Dans le second cas ils sont accompagnés d'un niveau haut en R2 et ne sont pas transmis en Q2.

Le réseau RC situé au niveau de Q<sub>1</sub>S<sub>1</sub> évite les rebondissements en Q<sub>1</sub>, principalement aux fréquences élevées.

Fig. 6. – Mélangeur modifié.

Chacun des comparateurs de phase est complété par une source de courant à trois niveaux. Le courant injecté dans le filtre de boucle, réseau RC, est + 1, - 1, ou nul suivant que la sortie PC<sub>out</sub> du comparateur de phase est au niveau haut, bas, ou dans l'état haute impédance. De cette manière, les performances du comparateur de phase sont indépendantes de la tension de contrôle, et, par là, de la fréquence de travail. Il se comporte alors, dans le modèle linéaire, comme un intégrateur de constante de gain :

$$K_{c} = \frac{1}{2\pi C} \tag{4}$$

où on désigne par 1 le courant de la source tri-état et C la capacité du filtre de boucle.

La résistance R de ce même filtre introduit un zéro en  $p = -\frac{1}{RC}$  nécessaire à la stabilité de la boucle (boucle de type 2, d'ordre 2).

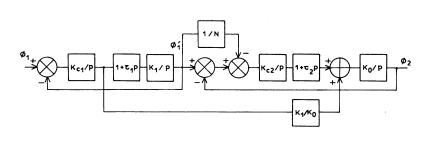

Le modèle linéarisé de la boucle complète est représenté par la figure 8 sur laquelle les constantes de gain des comparateurs de phases sont  $K_{c1}$ ,  $K_{c2}$ , les constantes de gain des VCO sont  $K_1$  pour le contrôle principal (par VCO<sub>in</sub>) et  $K_0$  pour le contrôle auxilliaire du second VCO par  $V_{aux}$ ). Les phases dynamiques à l'entrée, en sortie du premier PLL puis du second sont recpectivement  $\Phi_1$ ,  $\Phi'_1$  et  $\Phi_2$ .

Le gain bouclé du premier PLL est :

$$\frac{\Phi'_1}{\Phi_1} = \frac{K_1 K_{c1} (1 + \tau_1 p)}{K_1 K_{c1} (1 + \tau_1 p) + p^2}$$

(5)

que l'on écrit :

$$\frac{\Phi_1}{\Phi_1} = \frac{1 + 2\eta_1 \frac{p}{\Omega_1}}{1 + 2\eta_1 \frac{p}{\Omega_1} + \left(\frac{p}{\Omega_1}\right)^2}$$

avec :

$$\Omega^2_1 = K_1 K_{c1}$$

,

$$\tau_1 = 2\eta_1/\Omega_1$$

où  $\Omega_t$  et  $\eta_1$  désignent la pulsation propre et le facteur d'amortissement du PLL.

Le gain bouclé  $\frac{\Phi_2}{\Phi_1}$  du système entier est :

$$\frac{\Phi_2}{\Phi_1} \; = \; \frac{K_1 K_{c1} p^2 + \frac{N-1}{N} \, K_0 K_{c2} \, (\tau_1 \tau_2 p^2 + (\tau_1 + \tau_2) p \, + \, 1)}{(p^2 + K_1 K_{c1} \tau_1 p \, + \, K_1 K_{c1}) \, (p^2 + K_0 K_{c2} \tau_2 \, p \, + \, K_0 K_{c2})}$$

si l'on pose :

$$\begin{split} \Omega^2{}_2 &= K_0 K_{c2}, \\ \tau_2 &= 2\eta_2/\Omega_2, \end{split}$$

où  $\Omega_2$  et  $\eta_2$  désignent la pulsation propre et le facteur d'amortissement du second PLL, il vient :

système à condition que la fréquence propre du PLL reste très inférieure à la fréquence d'« échantillonnage » qui apparaît sur les entrées du comparateur de phase correspondant. Au-delà, on doit traiter

$$\frac{\Phi_2}{\Phi_1} \,=\, \frac{\Omega^2 \! \left[ p^2 + \frac{N-1}{N} \left( 4 \eta_1 \eta_2 p^2 + 2 (\eta_1 \frac{\Omega_2}{\Omega_1} + \eta_2) \Omega_2 p + \Omega_2^2 \right) \right]}{(p^2 + 2 \eta_1 \Omega_1 p + \Omega_1^2) (p^2 + 2 \eta_2 p + \Omega_2^2)}$$

Nous allons considérer, à titre d'exemple, le cas d'une boucle d'offset destinée à « suivre » une fréquence d'entrée sur une décade de fréquence, de 100 kHz à 1 MHz, avec  $N=1\,000$ . La fréquence d'offset,  $F_0=\frac{F_1}{N}$  varie de 100 Hz à 1 kHz.

Le modèle linéarisé représente correctement le fonctionnement du la boucle comme un système discret échantillonné.

Pour notre exemple, le premier comparateur de phase voit sur ses entrées, au verrouillage, une fréquence F<sub>1</sub> minimale de 100 kHz, pendant que le second voit la fréquence F<sub>0</sub> minimale de 100 Hz.

Il est donc raisonnable d'adopter pour les fréquences propres de chacun des PLL les valeurs respectives de 10 kHz et 10 Hz, soit :

$$\Omega_1 = 2\pi.10^4 \, \text{rad/s}, \tag{9}$$

$$\Omega_2 = 2\pi.10 \text{ rad/s}, \tag{10}$$

Indépendamment de ceci, il est important de noter que, suivant l'application particulière, une boucle PLL représentée par un modèle discret pourra exhiber des performances améliorées (temps d'acquisition réduit, rapport signal/bruit minimal...).

On a donc :

$$\Omega_1 >> \Omega_2 \tag{11}$$

Afin de minimiser les temps de réponse de chaque PLL, donnons-

## Technique de base \_\_\_\_

Fig. 8. - Modèle linéaire de la boucle d'offset large bande.

Fig. 9. - Modèle linéaire de boucle à « synthèse directe ».

nous pour les facteurs d'amortissement les valeurs :

$$\eta_1 = \eta_2 = \frac{\sqrt{2}}{2} \tag{12}$$

Compte tenu de (11) et (12), le gain bouclé (8) devient :

soit :

et

$$\tau'_1 = N\tau_1$$

$$K'_{cl} \simeq \frac{K_{cl}}{N}$$

$$\frac{\Phi_2}{\Phi_1} = \frac{N-1}{N} \, \frac{\Omega_1^2(\Omega_2^2 + \sqrt{2}\Omega_2 p + \sqrt{N-1})p^2)}{(\Omega_1^2 + \sqrt{2}\Omega_1 p + p^2)(\Omega_2^2 + \sqrt{2}\Omega_2 p + p^2)}$$

Comme N est très supérieur à l'unité, (13) se réduit à :

(14)

$$\frac{\Phi_2}{\Phi_1} = \frac{N-1}{N} \frac{\Omega^2_1}{\Omega^2_1 + \sqrt{2} \, \Omega_1 p + p^2}$$

La réponse du système est celle d'un filtre passe-bas d'ordre 2 du type Butterworth; elle est déterminée par les caractéristiques du premier PLL. Il est intéressant de comparer ce résultat à celui que donne une boucle de phase simple munie de divisseurs de fréquence (fig. 9). La réponse bouclée en est :

$$\frac{\Phi_2}{\Phi_1} = \frac{N-1}{N} \frac{\Omega'^2_1 + \sqrt{2}\Omega'_1 p}{\Omega'^2_1 + \sqrt{2}\Omega'_1 p + p^2} \quad (15)$$

$$\text{avec } \frac{\tau_1}{\tau'_1} = \frac{\Omega'_1}{\Omega_1} = \frac{1}{\sqrt{N}-1} \sqrt{\frac{\overline{K'}_{\text{c1}}}{K_{\text{c1}}}}$$

Comme le comparateur de phase voit maintenant sur ses entrées la fréquence  $\frac{F_t}{N}$ , on peut prendre :

$$\Omega'_1 = \frac{\Omega_1}{N}$$

La boucle de phase « à synthèse directe » présente des temps de réponse très supérieurs à ceux de la boucle d'offset correspondante. De plus, le diviseur inclus dans la boucle directe introduit un retard et un bruit de phase qui se retrouvent en sortie amplifiés du facteur de division.

#### **Performances**

La boucle d'offset (fig. 4) couvre la décade 100 kHz — 1 MHz. Le temps d'acquisition, à la mise sous tension est de l'ordre de 6 (charge de C<sub>2</sub> à courant l<sub>2</sub> constant). Le temps de réponse à un saut de phase de 180° est de 30 μs. Le bruit de phase en sortie est, exprimé dans le domaine temporel, de 20 ns crête à crête. Il est dû essentiellement au mode discret de fonctionnement du mélangeur.

G. N.

# P. FONTAINE

5 V - 1,5 A • 6 V - 1,5 A 12 V - 1,2 A • 15 V - 0,9 A 24 V - 0,5 A

Disponibles sur stock\*

DOCUMENTATION DETAILLEE SUR DEMANDE A: PIERRE FONTAINE ELECTRONIQUE 20, rue Arago, 91380 Chilly-Mazarin Tél.: 909.83.79 Télex: FONTEL 690254