# Comment choisir l'amplificateur de sortie pour les CNA multiplicateurs CMOS

Les Convertisseurs Numérique/Analogique (CNA) en technologie CMOS, depuis leur introduction sur le marché par Analog Devices en 1973, sont maintenant utilisés dans de très nombreuses applications. Leur possibilité de multiplication 4 quadrants ainsi que leur faible consommation et leur bas prix ont fait des produits de la série AD 7 500 un standard de l'industrie.

Bien qu'initialement limités à une précision de 10 bits, de récents progrès dans la technique de fabrication, et dans le réglage au laser au niveau du wafer (LWT), tant sur les CNA que sur les amplificateurs opérationnels, ont fait de la vraie précision de 12 bits une réalité. Pour conserver cette précision, l'utilisateur devra, au niveau du choix des composants associés, prendre certaines précautions que nous allons décrire ici.

L'utilisation d'un CNA CMOS requiert deux éléments externes.

Le premier est la référence. La technologie actuelle ne permet pas la fabrication d'une référence CMOS avec un bruit et une dérive suffisamment faibles pour un système 12 bits. Plusieurs CNA en technologie bipolaire, avec référence interne tels que les AD 565 A et AD 567 sont disponibles et même recommandés pour les applications à référence

fixe. Les CNA CMOS sont généralement utilisés lorsque la référence est un signal variable — que ce soit un signal continu modulé (exemple : commandes ratiométriques) ou un signal alternatif. Une réinjection capacitive parasite limite la fréquence maximum du signal de référence, mais la gamme audio est très facilement couverte dans sa totalité.

Ayant choisi un signal de référence, il reste à sélectionner l'amplificateur de sortie.

Pour les applications 8 et 10 bits avec une pleine échelle de 10 V, pratiquement n'importe quel amplificateur peut suffire. Par contre, si la référence (et donc, la pleine échelle) est réduite ou si une précision de 12 bits est désirée, le choix d'un bon amplificateur de sortie devient plus critique.

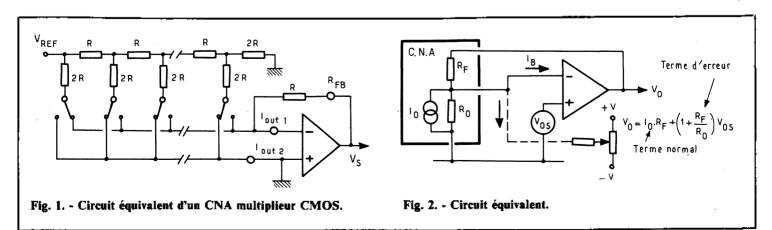

Considérons d'abord l'analyse en continu du circuit équivalent d'un CNA CMOS (fig. 1).

Pour ce circuit, utilisant un ampli OP idéal, nous avons :

$$V_s = -V_{REF} \times N$$

où N est le nombre binaire fractionnaire appliqué aux entrées numériques. Pour analyser les effets d'un amplificateur non idéal, examinons le schéma équivalent. Un examen attentif de la structure du réseau R-2R inversé montre que l'impédance d'entrée est constante (et égale à « R ») mais que l'impédance de sortie varie en fonction du nombre de bits à « 1 » (mais pas nécessairement de la position de ces bits).

Si seul le MSB est à 1 (courant s'écoulant dans le bus l<sub>out</sub> 1) R<sub>out</sub> est égale à 2 R. Si n'importe quel autre bit est mis à 1 seul, R<sub>out</sub> approche alors de 3 R. Si un nombre important de bits sont mis à 1, la résistance de sortie s'approche alors de R.

La figure 2 montre le circuit équivalent pour l'analyse des erreurs associées à l'ampli OP.

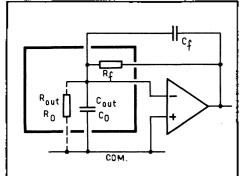

Fig. 3. - Amélioration de la stabilité de boucle par l'utilisation du condensateur de réaction C<sub>F</sub>.

Afin de minimiser le terme d'erreur de la figure 2, il est possible de réinjecter un courant i<sub>1</sub> de signe opposé, tel que :

$$V_{o} = i_{o} \, R_{F} + [V_{os} \, (1 \, + \! \frac{R_{F}}{R_{O}}) - i_{1} \, R_{F}]. \label{eq:Vos}$$

R<sub>o</sub> variant avec le code binaire, cette compensation ne pourra se faire que sur une valeur moyenne du terme d'erreur. La solution la plus efficace consiste donc à utiliser un amplificateur à très faible tension de décalage.

# Influence des caractéristiques d'entrée de l'ampli OP

La résistance de sortie variable du CNA crée un « gain de bruit » variable pour l'amplificateur.

Comme le décalage d'entrée peut être considéré comme un bruit en continu, il sera sujet à un gain variable, et ne restera donc plus un simple décalage. Même si le décalage a été ajusté à un code « tout à 0 », comme montré en figure 3, des erreurs de décalage variables sont induites plus haut dans l'échelle. Pour un 12 bits, ces erreurs peuvent facilement excéder 1 LSB. Considérons par exemple la transition de 1 bit de 001111111111 à 010000000000. La tension d'erreur en sortie change de 2 Vos à 4/3 Vos ; la variation incrémentale de l'erreur est de 2/3 Vos. Si Vos n'est pas de valeur négligeable, en tout cas plus faible que la tension équivalent au LSB, une erreur tangible sera constatée. L'effet pratique est l'introduction, non seulement d'un décalage, mais d'un terme d'erreur de non linéarité différentielle s'ajoutant ou se retranchant à toute non linéarité différentielle déjà présente. Si Vos est supérieur à 2,44 mV et de la polarité adéquate, la transition sera forcément non monotone : (donc une entrée numérique croissante se traduira par une sortie analogique décroissante), même pour un CNA parfait. (Note : ceci s'applique à un CNA 12 bits avec une pleine échelle de 10 V.) Ce problème est encore plus accru par le fait que beaucoup de convertisseurs manifestent leur plus mauvaise linéarité différentielle aux transitions majeures, lorsque beaucoup de bits tombent à 0 alors qu'un seul monte à 1. De la même manière, l'on doit également compter avec le courant de polarisation (I<sub>B</sub>) de l'amplificateur.

Le courant de polarisation de l'entrée inverseuse s'écoule à travers une résistance de valeur  $\frac{R_F\,R_{out}}{R_F\,+\,R_{out}},$

créant ainsi une légère tension de décalage. Ce décalage est amplifié par le gain de bruit,  $1+\frac{R_F}{R_{out}}$ , produisant une erreur de sortie égale à  $l_B$   $R_F$ , indépendante du code d'entrée. Ceci résulte donc en une simple erreur de décalage pouvant être annulée comme le montre la figure 2. Sans annulation, cette erreur peut être de 1 LSB pour un amplificateur ayant un courant de polarisation de 120 nA.

La résistance habituelle de compensation du courant de polarisation ne peut pas être introduite en série

avec l'entrée non inverseuse de l'amplificateur, car :

1) La combinaison parallèle de R<sub>F</sub> et R<sub>out</sub> varie de 25 % en fonction du code.

2) « R » peut prendre n'importe quelle valeur entre  $5 \, k\Omega$  et  $20 \, k\Omega$  d'un CNA à l'autre.

### Comment le gain en boucle ouverte de l'amplificateur peut affecter la linéarité de la conversion et le gain

L'équation traditionnelle d'erreur de l'ampli OP, lorsqu'elle est appliquée à un amplificateur de sortie de CNA CMOS, amène :

$$V_{o} = \frac{-\frac{(gain programmé)}{1 + \frac{1}{A_{o}\beta}}$$

où le « gain programmé » est le gain

déterminé en numérique, D; Ao est le gain en boucle ouverte de l'amplicateur; et \( \beta \) est la fraction de la sortie qui est réinjectée via l'atténuateur formé par R<sub>F</sub> et R<sub>o</sub>. β est la réciproque du « gain de bruit » mentionné au début de cette note, et est par conséquent affecté par le code numérique d'entrée, de la même manière que précédemment. Par conséquent, l'importance du terme . (idéalement zéro) peut varier de 1 A pour un gain programmé de zéro, jusqu'à  $\frac{2}{A_o}$  pour des codes conte-(0,02 %). Si Ao n'est pas suffisamment grand, le résultat peut être une augmentation de l'erreur de linéarité différentielle, en plus de toute erreur inhérente au CNA lui-même. Pour des applications 12 bits, un gain en boucle ouverte de 80 dB donnera une erreur légèrement inférieure à 1/2 LSB.

# Un amplificateur « ordinaire » n'est pas suffisant

Les multiples problèmes exposés ici peuvent être évités par un choix soigneux de l'amplificateur de sortie. Les modèles ordinaires ne sont pas suffisamment « bons » pour des applications 12 bits (ou des applications avec des tensions de référence réduites). Un amplificateur tel que le 741 possède des courants de polari-

sation et tension de décalage trop importants pour être utilisés avec des CNA CMOS. De plus, beaucoup d'amplificateurs rapides ont un courant de polarisation de centaines de nano ampères et des tensions de décalage de plus de 10 mV.

Les récentes évolutions dans les procédés de fabrication ont permis d'approcher les caractéristiques de l'amplificateur idéal. Les techniques FET à implantation ionique, quelquefois appelées « Bi-FET » ont permis d'améliorer d'une façon significative les caractéristiques statiques sans sacrifier la bande passante des amplificateurs bipolaires. Par exemple, il est maintenant possible d'ajuster automatiquement au niveau du « Wafer » les tensions de décalage et leur dérive des amplificateurs simples ou doubles à entrée FET. Ceci procure à l'utilisateur une simplification de mise en œuvre et de meilleures performances à un moindre coût. Voici quelques exemples de performances d'amplificateurs récente : technologie AD 547 LH a une tension de décalage et une dérive de 0,25 mV et 1 μV/°C respectivement, un gain en boucle ouverte de 250 000 V/V, un courant de polarisation de 25 pA max à la température de fonctionnement; le AD 544 LH a une bande passante de 2 MHz et une vitesse de montée de 13 V/µs avec une tension de décalage de 0,5 mV et une dérive de 5 μV/∘Ć.

### Aspects dynamiques

Nous avons amplement détaillé la réponse des amplificateurs à entrée FET en continu. Les performances en alternatif des CNA CMOS et de leurs amplificateurs associés doivent aussi être examinées. La sortie du CNA peut être modélisée par un réseau RC parallèle, où R et C sont dépendants du code d'entrée. Le

pôle en boucle ouverte formé par R (10 k à 30 k $\Omega$ ) et C (30 à 120 pF) peut tomber en dessous du point gain unité du sytème, et provoquer ainsi un déphasage excessif et ses problèmes inhérents d'accrochages ou d'oscillations. Ces difficultés peuvent être évitées en introduisant un zéro dans la boucle ouverte avec un condensateur en parallèle sur la résistance de contre-réaction (RF) et formant un atténuateur compensé en fréquence.

Il est souhaitable d'utiliser un condensateur CF de valeur aussi faible que possible, car de fortes valeurs réduisent la bande passante (et nécessairement le temps d'établissement).

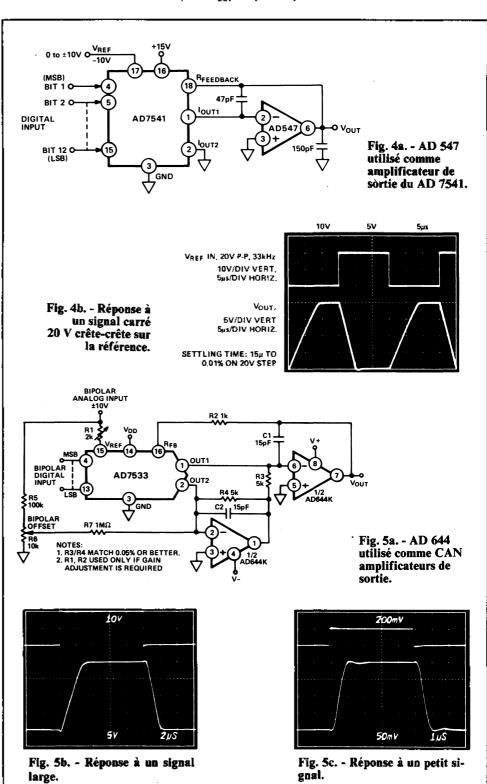

La figure 4a illustre ce qui précède et montre le AD 547 utilisé en amplificateur de sortie d'un AD 7541 monté en configuration unipolaire (multiplication 2 quadrants). Avec une référence fixe (positive ou négative) sur la broche 17 du CNA, le montage fonctionne comme un CNA bipolaire classique. Avec un signal variable sur cette broche, il fonctionne en multiplication 2 quadrants (atténuateur contrôlé numériquement).

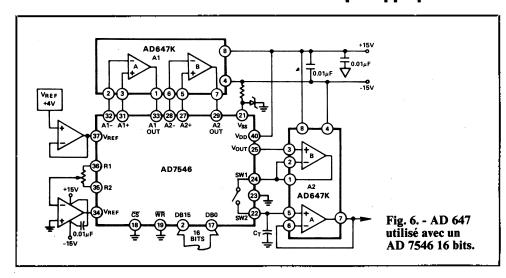

Les oscillogrammes de la figure 4b montrent la réponse du circuit de la figure 4a à un signal 20 V crête-crête à 33 kHz appliqué sur la broche 17 tous les bits étant à 1 (gain de 1-2-n). Le temps de réponse à ± 0,01 % est de 15 μs. Comme indiqué précédemment, la capacité de 47 pF sur la résistance de contreréaction est destinée à compenser la capacité de sortie du CNA. La capacité de 150 pF sur la charge est destinée à réduire les pics de « feedthrough ». Les figures 5 et 6 montrent 2 autres applications, l'une avec le AD 644 et le AD 7533 en configuration bipolaire (multiplication 4 quadrants) l'autre avec le AD 647 utilisé avec le AD 7546 16 bits.

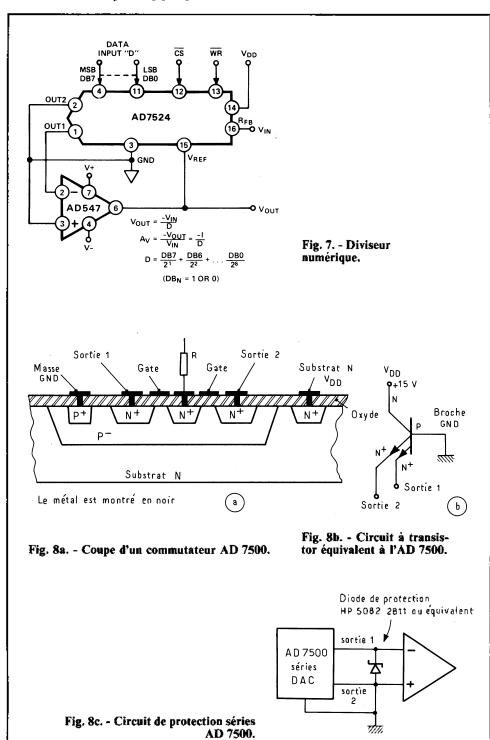

lement, OUT 1 et OUT 2 sont à la masse (ou à une masse virtuelle) et la fonction N+P- n'est pas polarisée. Cependant si OUT 1 ou OUT 2 est portée à un potentiel négatif inférieur à -0,7 V, le transistor NPN devient passant. Le courant collecteur qui n'est limité que par les possibilités de l'alimentation ou de la source reliée à OUT 1 ou OUT 2 va échauffer le circuit et risque de l'endommager ou de le détruire. On ne peut garantir que le point de sommation de l'amplificateur soit en permanence à la masse virtuelle. De nombreux amplificateurs bipolaires rapides présentent une faible impédance vis-à-vis de Vs- pendant les phases de mise sous tension ou hors tension, ce qui se traduit par l'apparition au point de sommation d'une tension négative inférieure à -0,7 V. Pour éviter de détruire le CNA, il est alors nécessaire de prévoir une diode Schottky comme indiqué en 8c.

Les amplificateurs à entrée FET ne présentent pas cet inconvénient et par conséquent ne nécessitent pas de diode Schottky comme on peut le remarquer sur les figures 4 à 7.

Nous remarquerons enfin, que sur certains CNA modernes tels que les AD 7524, AD 7533, AD 7541 A, AD 7542, AD 7545 de *Analog Devices*, l'effet du transistor parasite décrit ci-dessus a été supprimé et les diodes Schottky de protections ne sont plus nécessaires.

En ayant présentes à l'esprit les précautions indiquées ci-dessus l'utilisateur obtiendra les meilleures performances des CNA CMOS et évitera des pertes de temps coûteuses lors de la mise au point des montages.

Les CNA CMOS sont également largement utilisés dans des applications de contrôle numérique de signaux audio.

Dans de telles applications, la distorsion apportée par le CNA est négligeable et ce sont les caractéristiques de l'amplificateur de sortie qui détermineront les performances globales du système. Les AD 544 et AD 644 en particulier ont acquis leurs lettres de noblesse en prouvant leur excellente qualité en tant qu'amplis OP audio. Les amplificateurs à entrées bipolaires ne sont généralement pas adaptés étant donné leur courant de polarisation

généralement de l'ordre de plusieurs nano-ampères voire de l'ordre du micro-ampère ainsi que leur limitation en vitesse. Les AD 544 et 644 n'ont pas ces inconvénients. De plus, ces amplificateurs ont un autre avantage que nous allons décrire cidessous.

La figure 8a ci-dessus montre la coupe d'un commutateur canal N, SPDT utilisé dans de nombreux CNA CMOS. Sur le schéma équivalent du transistor donné en 8b, on remarque un transistor NPN parasite à double émetteur, dont la base est à la masse et le collecteur à V<sub>DD</sub>. Norma-

## Dans **Toute** l'Electronique

En mai:

L'oscilloscopie

Photon 83